# Service Manual

KENWOOD

T

# DG-5

Downloaded by Amateur Radio Directory

www.hamdirectory.info

Scanned by Ward Willats KG6HAF 17 August 2002

DIGITAL DISPLAY

# DG-5

## CONTENTS

| SPECIFICATIONS               |       |   |          |             |           | 3  |

|------------------------------|-------|---|----------|-------------|-----------|----|

| BLOCK DIAGRAM                |       | , | • • •, • |             |           | 4  |

| GENERAL                      |       |   |          |             |           | 5  |

| FUNCTIONAL DESCRIPTION       |       |   |          |             |           | 6  |

| CIRCUIT DESCRIPTION          |       |   |          |             |           | 8  |

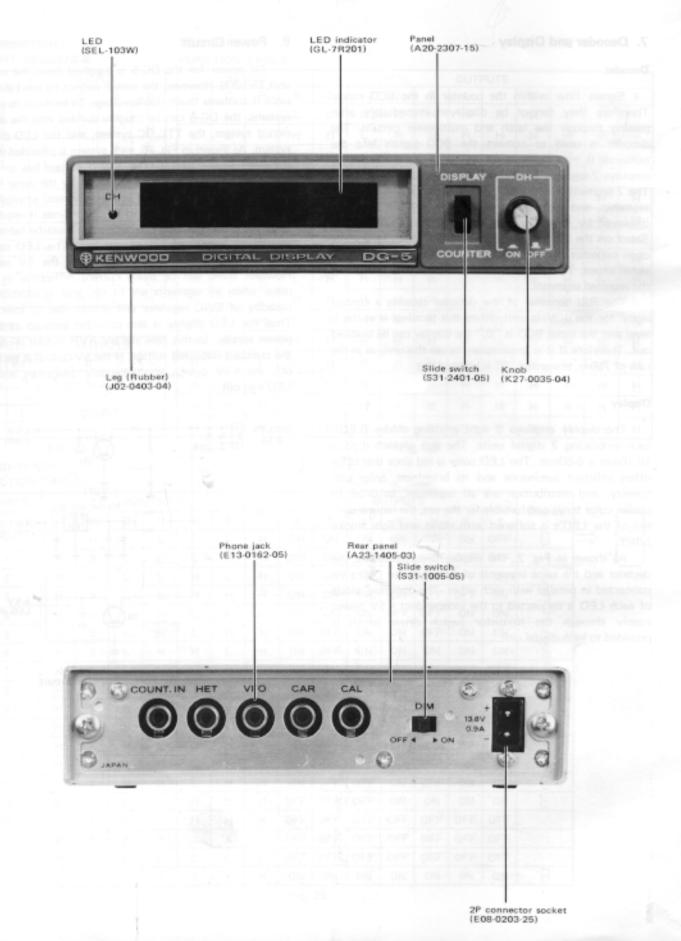

| EXTERNAL VIEW                |       |   | ••••     |             | • • • • • | 24 |

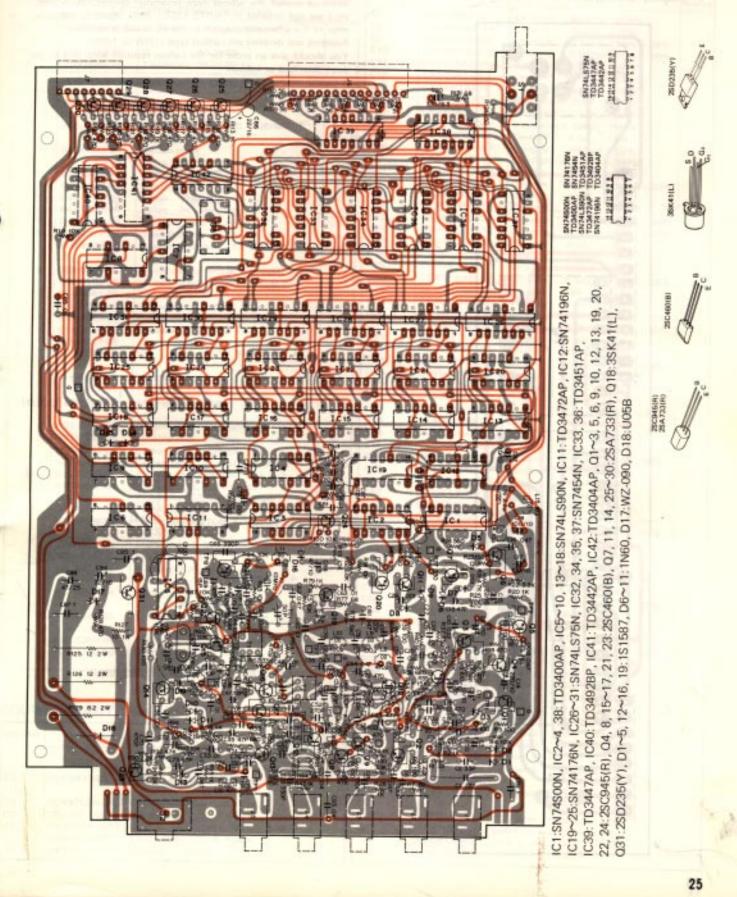

| PC BOARD                     |       |   | . •      |             |           |    |

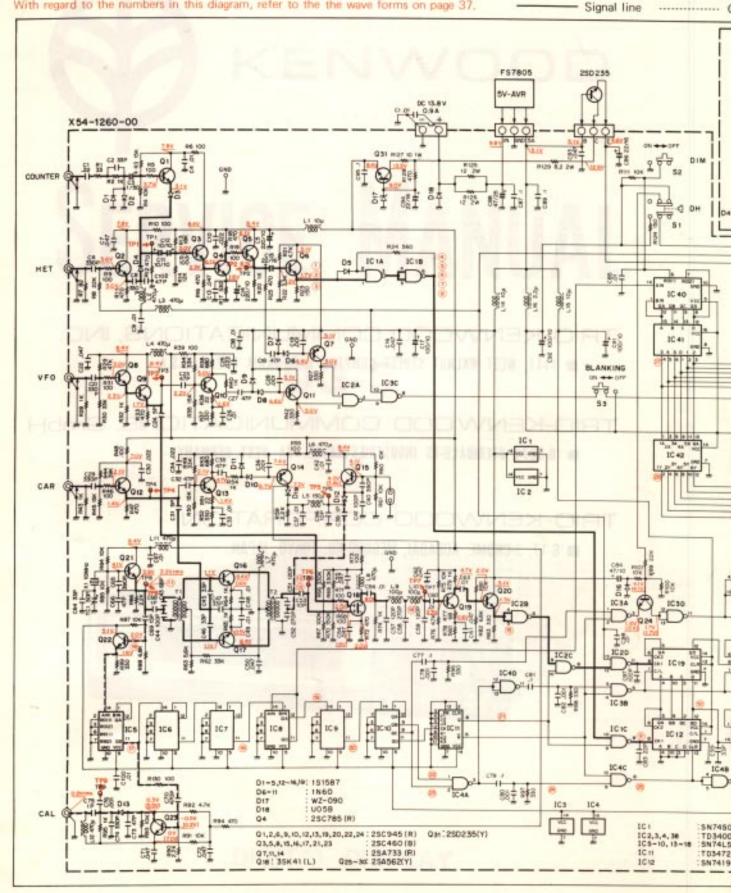

| COUNTER UNIT (X54-1260-00) . |       |   |          | • • • • • • |           | 25 |

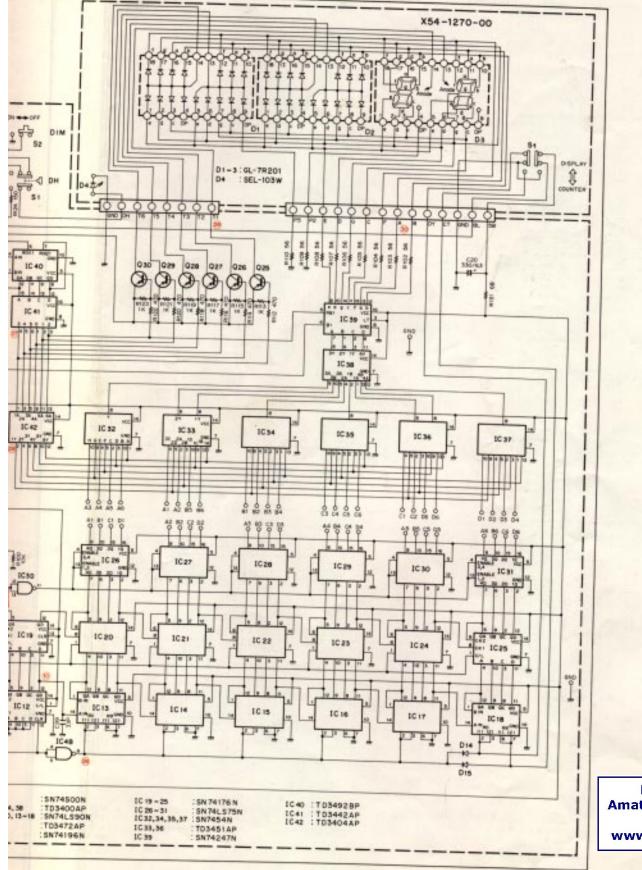

| DISPLAY UNIT (X54-1270-00) . | ••••• |   |          |             | • • • • • | 26 |

| PARTS LIST                   |       |   |          |             |           | 26 |

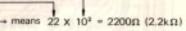

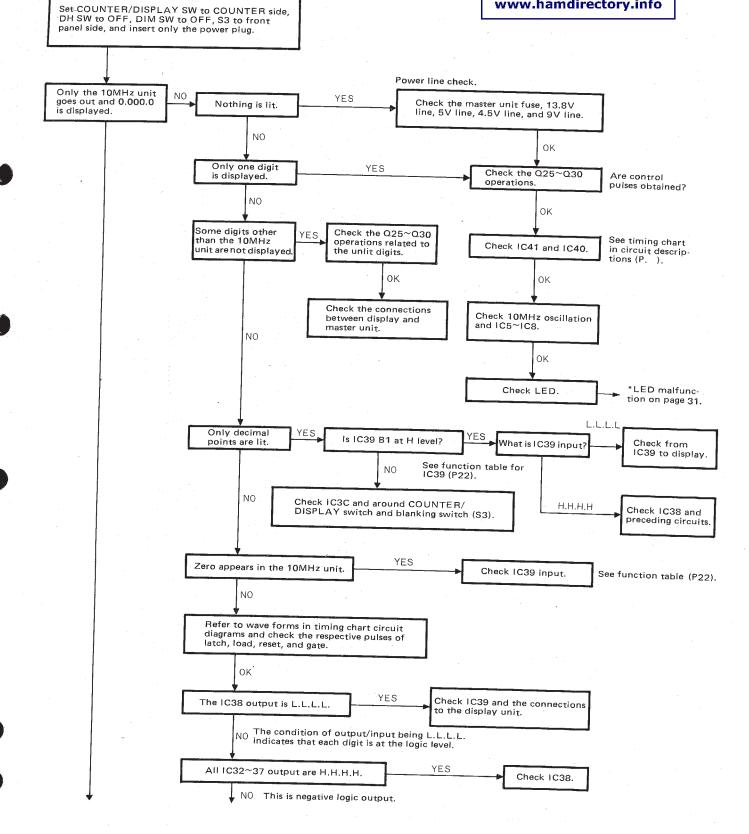

| TO OUR F SUCOTING            |       |   |          |             |           | 29 |

| LEVEL DIAGRAM                |       |   |          |             |           | 32 |

| ADJUSTMENTS                  |       |   |          | • • • • •   |           | 36 |

| SCHEMATIC DIAGRAM            |       |   |          |             |           | 38 |

|                              |       |   |          |             |           |    |

D

## SPECIFICATIONS

Countable Digits Type

DISPLAY (in combination with TS-520S) Frequency Range

Accuracy Input

## COUNTER

Measurable Frequency Range Input Sensitivity (at Room Temperature) Absolute Max. Input Level Input Impedance Accuracy Count Time Least Significant Digit

## **REFERENCE TIME**

Frequency Error Temperature Stability Aging Rate

## GENERAL

Ambient Temperature Power External Power Dimensions

Net Weight Semiconductors Used Six decimal digits. Light-emitting diode frequency display with hold memory.

All TS-520S transmit and receive channel frequencies as precise as 0.1 kHz digit. Reference time  $\pm 0.2$  count. TS-520S heteryodne local oscillator signal, VFO signal, and all carrier oscillator signals.

100 Hz to 40 MHz 50 mV r.m.s. at 10 kHz to 10 MHz 200 mV r.m.s. at 100 Hz to 40 MHz 200V (DC + peak). 5V r.m.s. (continuous at 100 Hz to 40 MHz). Approx. 5 k $\Omega$ , less than 22pF. Reference time ±0.1 count. 0.1 sec. 0.1 kHz.

10 MHz Less than  $1 \times 10^{-5}$  (at room temperature). Greater than  $3 \times 10^{-5}$  (at 0°C to +50°C). Lower than  $1 \times 10^{-6}$ /month (at room temperature).

-10°C to +50°C.

Supplied from TS-520S.

12 to 16V, 0.9A DC (with 13.8V reference).

167mm (6-9/16") wide × 260 mm (10-1/64")

[268mm (10-1/16"), max.] deep × (1-37/64")

[43mm (1-11/16"), max.] high

1.27 kg (2.8 lbs.)

42 ICs, 31 transistors, 19 diodes, 3 two-digit LEDs, and

1 LED indicator.

Downloaded by Amateur Radio Directory

www.hamdirectory.info

DG-5

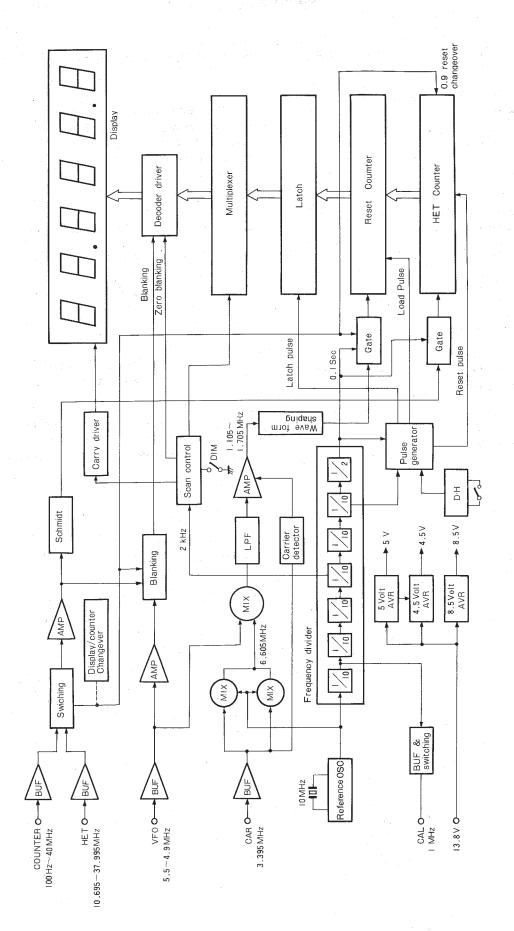

**BLOCK DIAGRAM**

Ø

Ð

٢

# 1. TS-520S, frequency perfectly readable in units of 100 Hz

All local oscillation frequencies (heterodyne, VFO, carrier) supplied from the TS-520S are used to synthesize display frequencies. The true transmitting/receiving frequency is accurately displayed in units of 100Hz. No corrections by band or mode changeover, calibration, etc., are required.

# 2. Can be used as a frequency counter (up to 40MHz) by a single-touch changeover motion

With the operation of a switch on the front panel the DG-5 can be used as a frequency counter which covers frequencies up to 40MHz. This changeover is acomprished by a single touch. In this setting it functions as a measuring instrument, and in this case also the smallest unit of measured frequency is 100Hz.

# 3. Thin construction for compact combination with the master unit transceiver

The total thickness (with rubber legs) is only 43mm, and the width is 167mm. Because of its very thin construction, when combined with the master unit (transceiver) it gives the appearance of a single unit, and the esthetic quality is therefore good.

## 4. Large, easily discernible LED frequency display, with dimmer switch

Since a large, easily discernible LED display is used, this unit can be used as an independent display or a frequency counter. The LED's are provided with color filters and the dimmer switch can be used to reduce the LED brightness. This permits comfortable operation without any accompanying fatigue even when it has been operated for a long time or at night.

#### 5. Easy connection with the master unit

By the use of the modified digital unit DK-520, it can be connected with either the TS-520. It can be easily connected with the TS-520S, through the 3-pin plug cord and the power cord. When making connection with the TS-520, the exclusively modified digital unit DK-520 must be added.

# Easy checking and repair are possible, facilitated by the completely non-wire system.

The DG-5 is composed of the main printed circuit board (counter unit), the display (display unit), the right and left frames, and the front and rear panels. This construction, devoid of wiring, permits very simple checking and repair.

## FUNCTIONAL DESCRIPTION

#### 1. Configuration

The DG-5 is connected with its master unit, TS-520S for the main purpose of digital display of the transmitting of receiving frequency. By changing over, it is also available as a frequency counter of 100Hz to 40MHz. The thin body (43mm in height and 167mm in width) and the large digit size (approx. 10 x 7mm) utilizing 6 large LED's provide a very satisfactory external display.

The electrical configuration of this unit is as shown in the block diagram on page 4. The unit consists mainly of the input terminal, the buffer amplifier mixer unit, the digital counter, and the display unit. Power is supplied from the master unit, TS-520S.

For frequency display performance, the 3 types of local oscillation signals – heterodyne (HET), VFO, and carrier (CAR) – are taken from the master unit and mixed with the 10MHz source from the counter's reference oscillator. Since an additional 2 counters are employed and the frequency display component is synthesized in the analog/digital mode, undesirable effects upon the master unit such as spurious disturbance can be minimized.

For frequency counter performance the input circuit is changed over to the counter terminal by means of the diode switch, and the input signal is counted and displayed through the HET counter indicated in the block diagram.

In the counter section the standard frequency of 10MHz is frequency-divided down to 5Hz to obtain a reference gate time of 0.1 second. Though the smallest unit of display is 100Hz, the counter counts the frequency in units of 10Hz; therefore there is minimal fluctuation in the 100Hz units. Since the latch interval is 0.2 second,

fluctuation is minimal during dial operation. This latch interval is correct for the operating speed. Each large-size LED on the display unit is provided with both a violet and a light smoke filter with transmission rates of 82%, thus providing a comfortable tone and an adequate luminous intensity.

#### 2. Principle of Display Frequency Synthesis

In order to compose a frequency component for display, the DG-5 takes the HET (heterodyne), VFO, and CAR (carrier) frequencies from the master unit. In addition to the analog unit, the DG-5 employs 2 digital counter circuits for the digital synthesis, by which the desired display signal is obtained.

In the TS-520S the 3 local oscillation frequencies are mixed to synthesize the transmitting/receiving frequency under the following conditions:

HET -- (VFO + CAR) ..... (1)

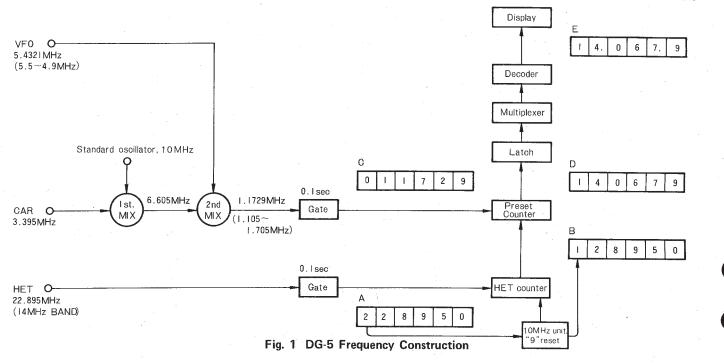

Though the display frequency can be composed by the same process, generation of the same frequency as that in the master unit is undesirable because of the existence of spurious disturbance. Hence a digital process is added in order not to produce a frequency which is analogously the same as that of the master unit. Fig. 1 shows the DG-5 frequency configuration through an example of the 14MHz band. The following explanation follows those actual figures.

The HET signal of 22.895MHz passes through the 0.1 second gate and is counted by the HET counter in units of 10Hz. In the HET counter the reset signal is applied to the "R9" terminal only for a unit of 10MHz and the output is reset at "9." Therefore, with an initial state of 9 in the

## FUNCTIONAL DESCRIPTION

10MHz unit, each time one pulse inters, the output shows a digit which is always smaller by one than the number of input pulses. That is, as shown in Fig. 1, the 10MHz unit of the HET counter input A 228950 loses "1" and the output B is shown as 128950. The squares show the input/output component of each digital unit ranging from the 10MHz unit to the 100Hz unit for the decimal counter. The respective digits of the output B of the HET counter are preset by the preset counters that are connected in series with the respective digital units.

The CAR signal of 3.395MH z is mixed with the reference oscillator signal of 10MHz at the first mixer and is converted to a frequency of 6.605MHz. This signal is further mixed with the VFO signal (5.4321MHz in Fig. 1) at the second mixer and is finally converted to a frequency of 1.1729MHz. This signal passes through another gate circuit and is counted by the preset counter in units of 10Hz.

In addition to the signal input terminal, the preset counter is provided with the preset input terminal to which an external BCD signal is applied to preset the initial state of the counter to an arbitrary value. The output is the sum of this preset value and the number of input signal pulses. In the DG-5 the output B of the HET counter 128950is preset by the preset counter. Therefore the preset counter output is the output D 140679, which is the sum of the preset value B and the input signal counter component C 011729. This output D further passes through the latch, multiplexer, and decoder, and the correct frequency is indicated at the display E in the form of (14.067.9). Thus the display frequency synthesizing process in the DG-5 is as follows:

(HET - 10) + (10 - CAR) - VFO = HET - (VFO + CAR) (2)

The above result is identical with the frequency relationship in the master unit, and the displayed frequency exactly coincides with the frequency of the master unit. The difference is that the analog block does not generate any frequency which causes direct interference with the transmitting/receiving frequency, IF frequency, etc. of the master unit. Therefore, even when the DG-5 is connected, the occurrence of direct beat trouble, spurious disturbance, etc., can be avoided.

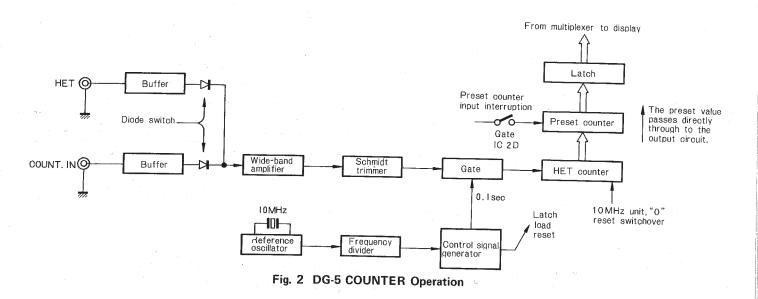

## 3. Frequency Counter Operation

The frequency counter of the DG-5 is fundamentally used to read out the frequency of a measured signal which has been inputted to the HET counter. Fig. 2 shows the basic section. The signal to be measured is applied to the COUNT IN terminal on the rear panel. After passing through the buffer circuit, either the HET signal input or the signal to be measured is selected by the diode switch. The circuit after the wide-band amplifier is used in common with the HET signal. The signal finally enters the HET counter.

Though the HET counter is actuated by resetting the 10MHz unit at "9" during display operation, it operates in the "0" reset mode during frequency counter operation so that the input pulses can be directly indicated as an output.

In this case the preset counter is merely used to send out the HET counter preset value immediately to the output circuit. Therefore the gate circuit before the input terminal is switched over so that the signal input can be interrupted. Thus the frequency counter operation is equivalent to the condition that the frequency counted at the HET counter is directly displayed.

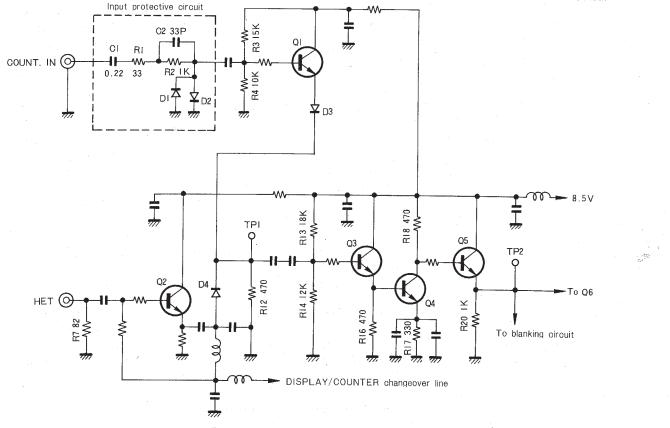

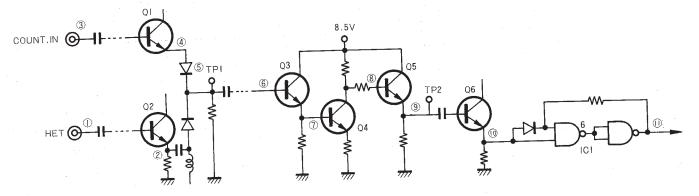

#### 1. HET/Counter Amplifier

#### Input Circuit

DG-5

The HET terminal receives an HET signal of 10.695  $\sim$  37.995MHz from the HET oscillator of the TS-520S through the 75 $\Omega$  coaxial cable. Therefore the terminal resistor 82 $\Omega$  is connected and the HET terminal is connected to Q2 to obtain a buffer effect. The Q2 amplifier is arranged in an emitter follower connection.

The COUNT. IN terminal is also connected to the emitter follower type buffer amplifier consisting of Q1 to avoid being affected by the external circuit which is connected with a measuring cable. Since the frequency to be handled may range widely from 100Hz to 40MHz and the internal circuit must be protected against excessive input, there is an input protective circuit as shown in the dotted-line box in Fig. 3. This input protective circuit consists of the CR series-parallel circuit and the diode clamper. As the input voltage begins to increase in the initial state of operation, Q1 is applied with a voltage which is divided by R1 and R2 together with the input impedance (about  $5k\Omega$ ) in the rear stage. If this voltage is higher than the potential difference (about 0.65V) between diodes D1 and D2, current begins to flow into the diode and a higher voltage above the threshould level cannot be applied to Q1. This phenomenon is inevitably a protective operation for the input circuit. The capacitor C1 is used for DC interruption, while capacitor C2 is used to prevent reduction in sensitivity by permitting the flow of high frequencies through the resistor R2, since the sensitivity will suddenly decrease at 10MHz or more because of the existence of the input capacitor. The limit of input voltage is  $50 \sim 100V$  in a low-frequency band not higher than 2MHz. Since there is a decrease in the series resistance component at higher frequencies due to the effect of C2, withstand voltage decreases at the rate of 6dB/oct and is finally about 5 volts at 40MHz. If this limit is exceeded, the resistor R1 is designed to burn out.

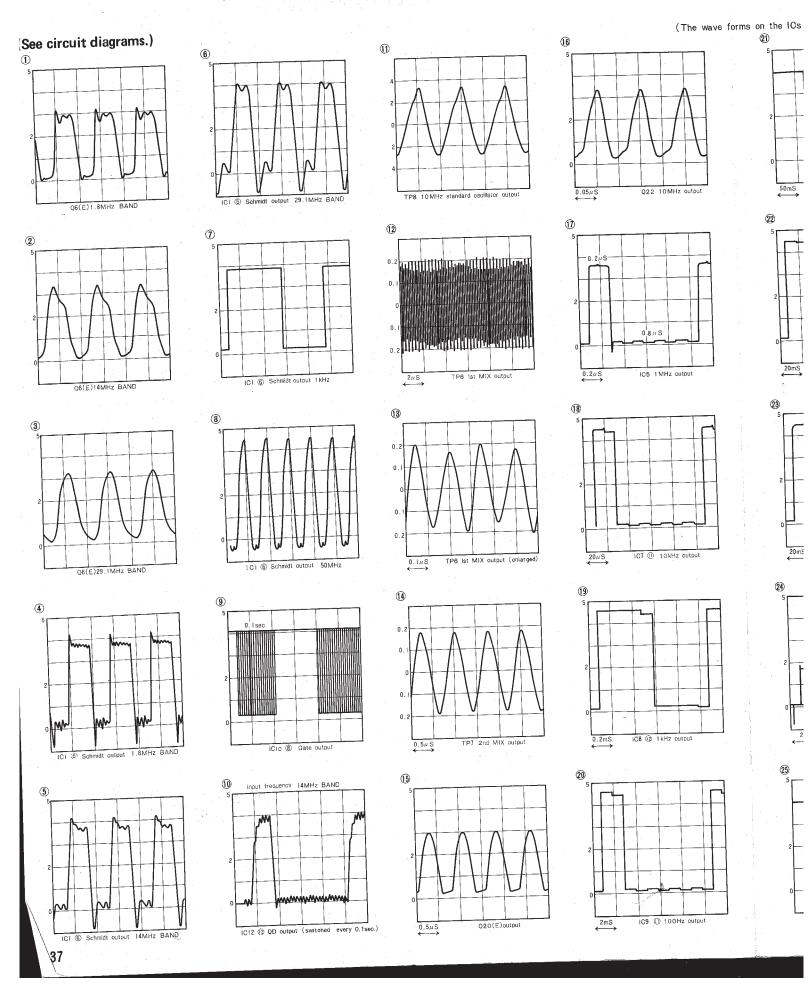

#### Wide Band Amplifier

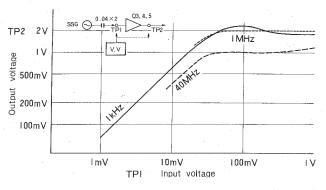

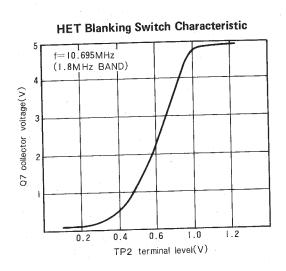

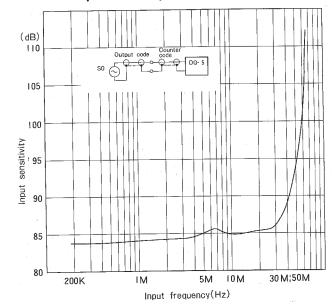

The input signal passing through the emitter follower circuit and the diode switch is amplified at the wide-band amplifier consisting of Q3  $\sim$  Q5. Since this block disposes of a very wide frequency range of  $100 \text{Hz} \sim 40 \text{MHz}$ , the transistor Q4 composes an amplifier with a collector load impedance of 470 $\Omega$ , which is very low. At the same time both the input and output circuits are connected with the directly-coupled emitter follower circuits to avoid the effect of the former and latter stages. Thus the resultant gain is about 30 to 35dB between TP1 and TP2 throughout the frequency range. This amplifier has the input-output characteristic shown in Fig. 4, and in actual counting conditions it operates in an almost saturated zone. Therefore the apparent gain between the HET terminal and the TP2 is 15 to 20dB during actual operation when measured with a voltmeter and with the master unit connected.

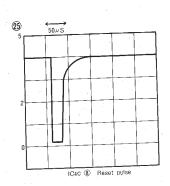

Fig. 3 HET/COUNTER AMP

Fig. 4 Characteristic of Wide Band Amplifier

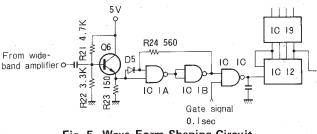

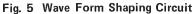

#### A/D Coupling Circuit and Schmidt Trigger Circuit

The wave form of a sufficiently amplified signal is pulse-shaped by the circuit shown in Fig. 5 and is then applied to the counter gate circuit. The transistor Q6 is a coupling circuit located between the analog system of the preceding stages and the 5V power supply system of the TTL. IC in the successive stages. Since the H and L level values of the TTL. IC are restricted by the power supply voltage of 5 volts, the power supply voltage of Q6 is also 5V. The Q6 circuit is arranged in an emitter follower connection since its output impedance must be low because of the characteristic requirement of the Schmidt circuit in the next stage.

The circuit consisting of IC1A  $\sim$  IC1B and D5 is Schmidt trigger or the wave form shaping circuit, which converts a gently changing wave form like a sine wave into a spulse wave. The counter circuit counts the number of input pulses. Since TTL. IC is arranged to operate under the restriction that the L level is 0.8V or below and the H level is 2.0V or above, the time necessary for switching over from L to H or H to L will increase if the rising and falling modes of the pulses are too gentle. If any noise enters during this time it will be counted as a pulse, thus leading to a mis-display.

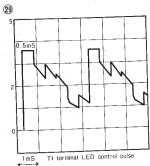

In the Schmidt circuit the output from Q6 is applied to the 2-input NAND circuit. This output is directly applied to one gate of the 2-input NAD circuit, and simultaneously it is applied to the other gate through the diode D5. In this case the output is not reversed unless both the 2 inputs attain the H level at the IC1A. Therefore, as shown in Fig. 6, the IC1A is not triggered unless the input voltage is

Fig. 6 Operation of Schmidt Trigger Circuit

higher than the sum of the D5 terminal voltage (about 0.65V) and the threshold voltage (a voltage at which the output suddenly changes from H to L, i.e. about 1.3V in terms of input voltage). The output caused as a result of reversal from H to L is again reversed by IC1B from L to H. The voltage reversed from L to H is positively fed back through the resistor R24 to the input gate of the first stage, which is provided with D5. Therefore, with the entry of even a gentle input a snap action takes place and a sharp rising mode is obtained. The falling mode is obtained similarly, but in the completely reverse order. In other words, this circuit has a hysteresis characteristic since there is a time lag in rising or falling performance by the amount of the terminal voltage component of D5. This voltage component is effective as a noise margin, as shown in Fig. 6.

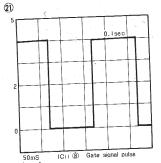

The ICIC is a signal gate circuit for the HET counter. This circuit permits the flow of pulses from the Schmidt circuit while there is a 0.1-second gate signal generated by the standard oscillator. For this 0.1 second the HET counter counts the number of pulses which have passed the gate.

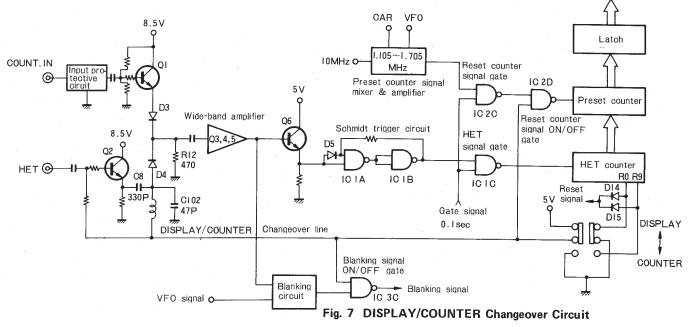

## **DISPLAY/COUNTER Changeover Circuit**

Both HET and COUNTER. IN signals are fed to the HET counter. Therefore either signal is selected with the changeover switch on the front panel. Fig. 7 shows an overall diagram of the DISPLAY/COUNTER changeover circuit. Changing over is performed by the aid of the output diode switches of the input emitter follower circuit, the input gate of the preset counter, the "9" and "0" reset circuits for the 10MHz unit of the HET counter, and the blanking ON/OFF gate.

With 5 volts applied to the desired side, a bias voltage is applied to Q2 and the diode D4 is turned on to change over the input emitter follower circuit to the HET side. If the line voltage decreases to zero the bias disappears from Q2, causing D4 to turn off and D3 to turn on. Thus Q1 functions and the circuit is changed over to the COUNTER side. The preset counter and blanking ON/OFF gates are switched off if their gate voltages become zero. At that time both the preset counter and blanking signals are interrupted and the circuit is changed over to the COUNT-ER side. In the HET counter circuit for the 10MHz unit the resistor R0 is grounded in the DISPLAY mode and the reset signal cannot be applied to their respective reset terminals.

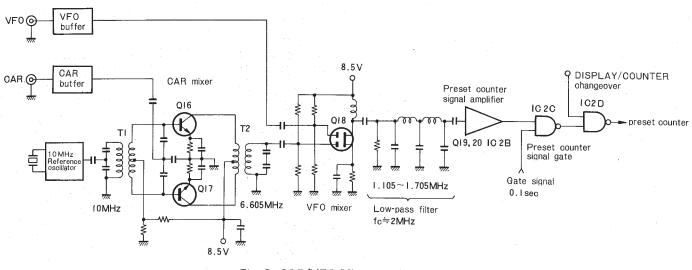

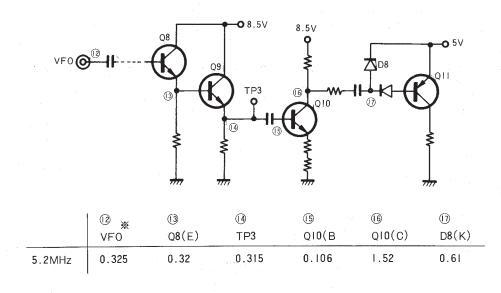

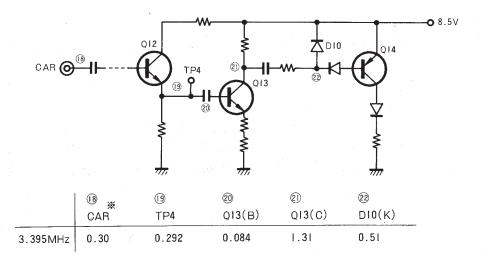

#### 2. CAR/VFO Mixer and Amplifier

#### Input Buffer

In order to avoid the effects of the preceding and succeeding stages, the VFO and CAR terminals are also provided with emitter follower type buffer amplifiers just as the HET terminal is. In particular, since the VFO buffer has the function of preventing reverse leakage into the master unit, it has 2 emitter follower stages in a Darlington connection.

#### CAR Mixer

The 3.395MHz carrier is mixed here with the 10MHz signal to obtain a 6.605MHz signal. If the input frequency leaks into the output terminal, it will give rise to a spurious component which causes of miscounting. Therefore Q16 and Q17 together with T1 and T2 are arranged to compose a balanced mixer which cancels the components in the same

phase. However, this type of mixer must not receive too much input; both carrier and 10MHz signals must be maintained at about 100mV. Taking the selectivity of the output coil T2 into account, the suppression level is about 40dB.

#### **VFO Mixer and Signal Amplifier**

The 6.605MHz signal is mixed at Q18 with the VFO signal of  $5.5 \sim 4.9$ MHz. The mixed output passes through the low-pass filter and is converted into a frequency ranging from 1.105 to 1.705MHz. This circuit is an ordinary FET mixer and the output from the low-pass filter is the lower side band only. Since the mixer output voltage is only 0.1 to 0.2V, it must be amplified by Q19 and Q20 to a level at which the TTL. IC can be actuated. The Q19 is an amplifier of about 20dB, while the Q20 is a coupling emitter follower circuit for the TTL. IC. The Q19 power supply is obtained from the carrier switching circuit. If there is no carrier input, the source voltage is interrupted and the effect of the amplifier disappears. Thus irregular and abnormal display due to leakage from the mixer can be avoided.

#### **Signal Gate Circuit**

The sufficiently amplified signal is shaped into a pulse wave through the inverter of IC2B and is then applied to the preset counter signal gate of IC2B. In this case the standard gate signal is applied for 0.1 second, and during this period the signal pulses are sent to the preset counter through the DISPLAY/COUNTER changeover gate. At this gate, a signal enters when a 5V input is applied to another input terminal of IC2B (in the display mode). The signal is interrupted when this terminal is grounded (in the counter mode).

Fig. 8 CAR/VFO Mixer & Amplifier

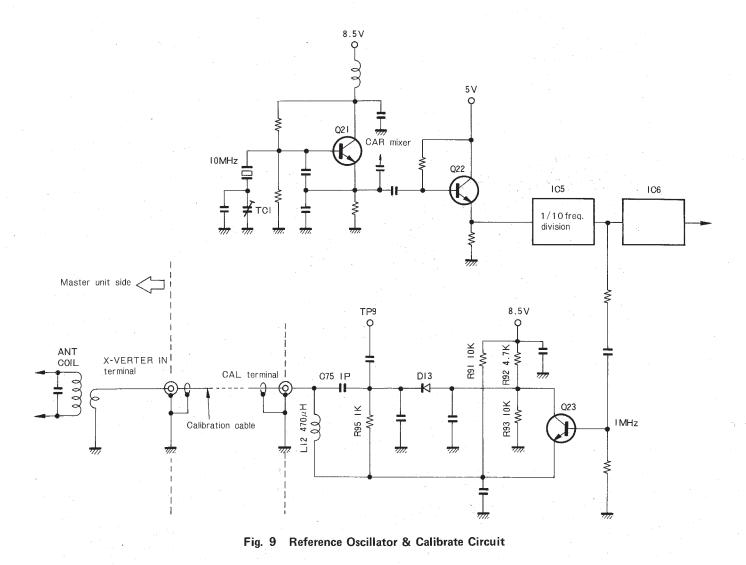

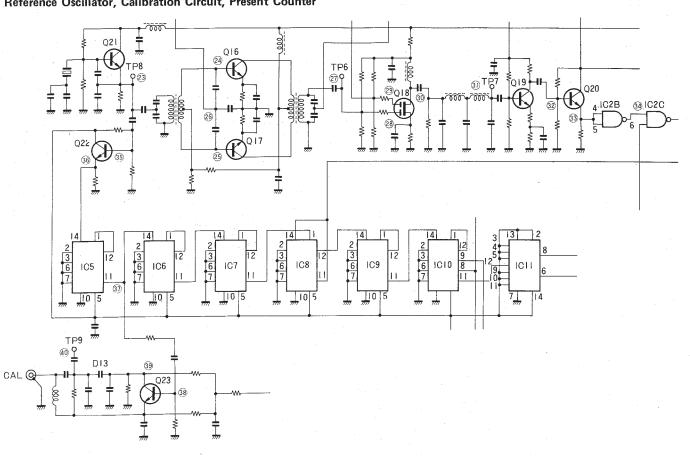

## 3. Reference Oscillator and Calibration Circuit

#### **Reference Oscillator**

The reference oscillator employs a 10MHz quartz crystal unit. Since the counter display accuracy depends on the accuracy of the 0.1-second standard time which is obtained by frequency division, the reference oscillator is so to speak the heart of the counter. The quartz crystal unit used here is obtained by cutting to obtain a zero thermal coefficient, and its accuracy is guaranteed to the 100Hz unit in actual use.

As shown in Fig. 9, the oscillating circuit is a Colpitts circuit which generates a sine wave to be fed to the CAR mixer. The Q22 buffer circuit is installed in front of the IC block, and output is supplied to the frequency divider to make a standard time of 0.1 second.

#### **Calibration Circuit**

The reference oscillator is of no use if it does not oscillate at 10MHz exactly. For calibration the standard waves of WWV, etc. are the most accurate and handy frequency sources. Since the TS-520S, can receive a standard wave of 15MHz (the TS-520, for 10MHz), the output circuit of the reference oscillator is extracted for calibration with the standard wave in combination with the radio receiver. This mission is accomplished by the calibration circuit consisting of Q23 and therafter. Since the standard wave to be received is 15MHz or 10MHz, the oscillator output is divided into 1/10 and 1MHz is taken out. Also in this case the wave form is rectangular with excessive harmonics, and this is favorable for calibration.

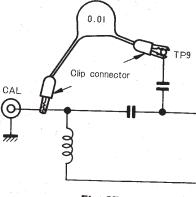

Q23 and D13 compose a buffer circuit for calibration output. This circuit also functions as a switch, and it does not operate unless the attached coaxial cable is connected to the CAL output terminal and the receiver calibration input terminal (X-VERTER IN terminal for the TS-520). If nothing is connected to the CAL output terminal of a circuit, as shown in Fig. 9, the potential at the Q23 emitter and the D13 cathode is unfixed and the source voltage of 8.5V is applied directly. Simultaneously the Q23 collector and the D13 anode are applied with a potential which is produced from the source voltage divided by R92 and R93. In other words, Q23 and D13 are reversely biased and a cut-off condition is maintained. Thus the 1MHz output does not appear at the CAL terminal. When the separately furnished calibration connection cable is connected to the X-VERTER IN terminal of the master unit, the DC component at this terminal is grounded through the coil. Therefore in this case the emitter of Q23 is grounded and Q23 is turned on. Simultaneously D13 is turned on through R19, which is a current limiting resistor. Thus the 1MHz output (including harmonics) appears at the CAL terminal and is fed to the receiver.

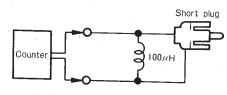

Fine frequency adjustment for calibration is made by the trimmer capacitor TC1 of the reference oscillator. When the frequency is adjusted with a more accurate frequency counter (meaningful only if its accuracy is more than  $10^7$ ), the CAL terminal is short-circuited and the counter is connected to the test point TP9.

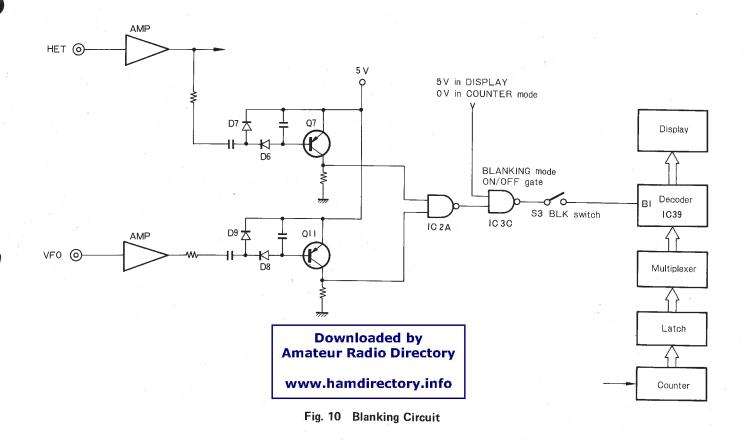

## 4. Blanking Circuit and Carrier Switching Circuit

#### Local OSC. Input Detection

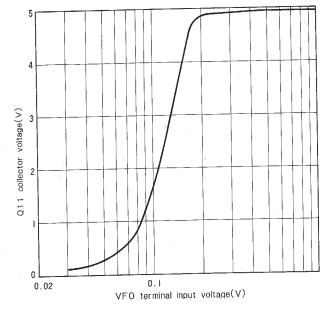

While the DG-5 is in operation in the DISPLAY mode, it is fed the three outputs of HET, VFO, and CAR from the master unit. However the supply of local oscillation output may be interrupted due to trouble in the master unit, cable or terminal malfunction, misconnection, or to setting the FUNCTION and BAND switches of the master unit at incorrect positions. If the display is unchanged in such a case it will give unstable and meaningless indications due to intrusion of noise. Therefore the DG-5 is devised to detect the presence of the outputs, HET, VFO, and CAR. If there is no HET or VFO input, a blanking signal is generated to delete the indication on the display (except for the decimal point). If the CAR input disappears, the source voltage is removed from the preset counter signal amplifier of Q19 in Fig. 8 so that the display cannot change.

#### . . .

**Blanking Circuit**

When either the HET or VFO input from the master unit disapperars, the blanking circuit sends out a blanking signal to the decoder IC to blank out the dispplay. Both HET and VFO signals are amplified in the circuit in Fig. 10 and the output is detected and rectified by the iodes. If the signal is present, Q7 and Q11 are turned on by the effect of the rectified voltage. The 2 inputs from IC2A are at the H level and the output is at the L level, the IC3C output is maintained at the H level regardless of the other input level This output is applied to the BI terminal of the decoder IC39 through the blanking switch S3. As shown in the function table of Fig. 25 for SN74247N, blanking is not performed at the H level under normal operating conditions.

When either the HET Or VFO signal disappears, the IC2A input on the no-signal side is at the L level and the output is turned to the H level. Therefore in the DISPLAY

mode two IC3C inputs are at the H level and the output is at the L level, and thus the BI terminal of IC39 is maintained at the L level. The function table in Fig. 25 indicates that the decoder output is switched off and the display is blanked out.

During COUNTER operation both HET and VFO signals disappear as a matter of course. In this case IC3C is used to avoid blanking. Either input is put at the L level in interlock with the changeover switch on the panel surface. Since the display should not be blanked out during adjustment and repair, the switch S3 is installed for blanking OFF.

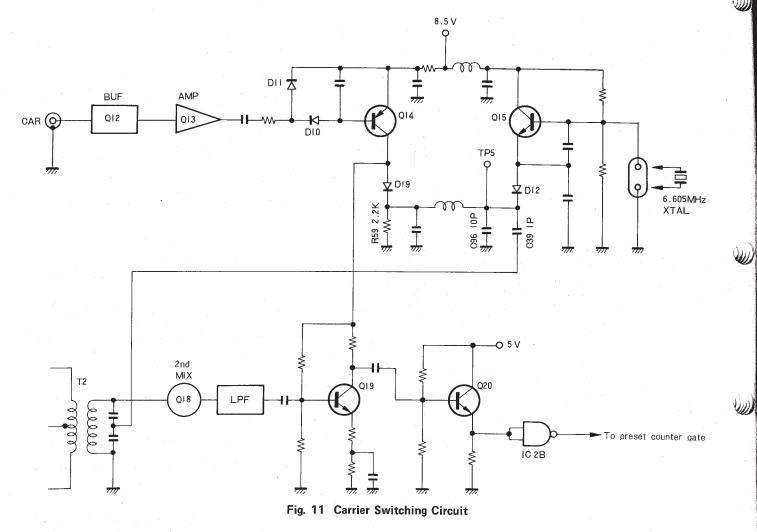

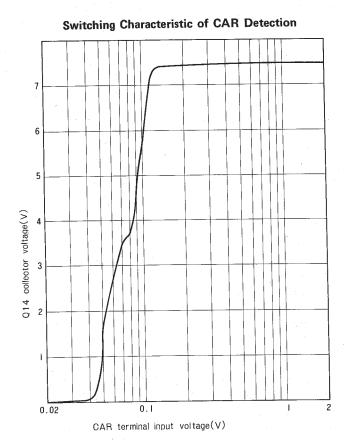

#### Carrier Switching Circuit

Like the blanking process for the HET and VFO inputs, the circuit in Fig. 11 detects the carrier with the diodes D10 and 11 and the transistor Q20. While the carrier signal is maintained at the input terminal, the source voltage is applied to the Q19 amplifier. If the carrier disappears, Q14 is turned off and the power supply is removed from Q19 to switch off the amplifier.

Q15 is a quartz crystal oscillator. When a 6.605MHz crystal unit is connected to the terminal and the carrier signal disappears, Q15 automatically begins to oscillate since the cut-off bias of Q14 applied to the Q15 emitter is lost. If an AM unit is connected with the DG-5, the carrier signal will disappear. Therefore, in place of this carrier signal, the oscillator output is fed to the input terminal of the VFO mixer. At that time the power is not supplied to Q19, and it is necessary to remove the connection to Q14 and to apply a separately obtained 8.5V to the Q19.

#### 5. Counter Circuit

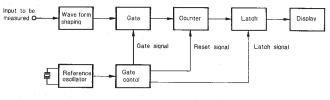

#### Principle of Frequency Counter

The general principle of the frequency counter is explained by the block diagram shown in Fig. 12. The input signal to be measured is amplified, shaped, and converted into pulses. The gate circuit is open for a predetermined time period which is based on the reference time. The pulses passing through the gate while it is open are counted at the counter block and temporarily memorized in the latch circuit. At predetermined intervals the memorzed information is sent to the display. The sequential order for the above is as follows:

- (1) With a reset signal the condition in the counter is made "0."

- (2) With a gate signal the gate circuit is open, and the counter begins to count the pulses which pass the gate.

- (3) When the gate signal disappears, the gate circuit is closed and the counter terminates its counting.

- (4) With a latch signal the counted value memorized in the latch circuit is transferred to the display unit where the result is displayed.

W

W

V

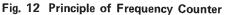

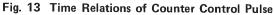

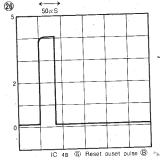

(5) Return to state (1) and the same sequence is repeated. The reset, gate, and latch signals control the respective blocks in proper sequence. As previously described for the principle of display frequency synthesis, the DG-5 is provided with an additional preset counter and the contents in the two counters are combined. Fig. 13 shows the time relationship for the control pulses. Compared with the case of Fig. 12, the load pulse (signal) is added and this is used for a preset command. The sequential order for the block diagram in Fig. 13 is as follows:

- (1) With a reset signal the condition in the HET counter is made "0."

- (2) With a gate signal the HC gate circuit is open and the HET signal pulses pass through the gate. The HET counter begins to count the pulses which pass the gate.

- (3) When the gate signal disappears, the HC gate circuit is closed and the HET counter terminates its counting.

- (4) With a load signal the preset counter is preset at the final counting value at the HET counter.

- (5) With a gate signal the PC gate is open and the PC signal pulses pass through the gate. The preset counter begins to count the passed pulses and to add the result to the preset value.

- (6) When the gate signal disappears, the PC gate is closed and the preset counter terminates its counting.

- (7) With the latch signal the preset counter value memorized in the latch circuit is delivered to the display unit where the result is displayed.

- (8) Return to state (1) and the same sequence is repeated. In this case the HC gate and the PC gate operate simultaneously with the same gate signal. As shown in Fig. 13, the cycles (1) to (7) advance together, but there is always an overlap of half a cycle between the neighboring cycles.

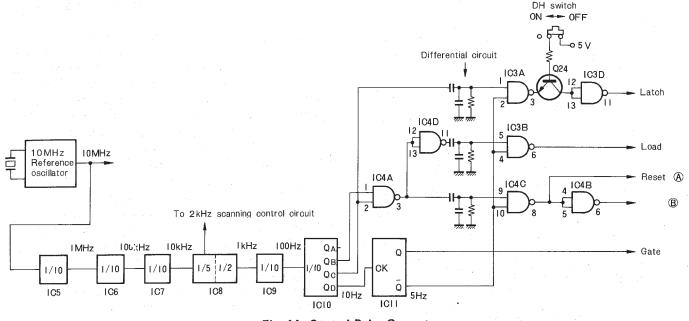

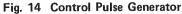

#### **Control Pulse Generator**

**DG-5**

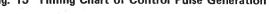

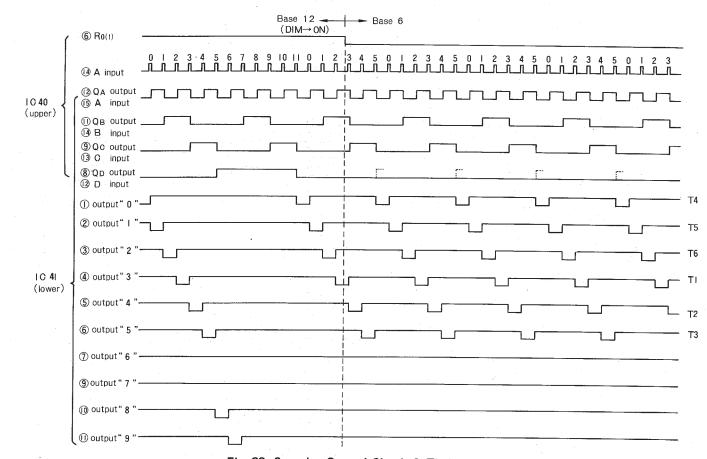

For the orderly control of the DG-5 gate and counter in Fig. 13, the control pulse generator is employed. Fig. 14 shows this circuit together with the frequency divider circuit. Fig. 15 shows the timing chart for explaining the operating condition. In Fig. 15, the 10MHz signal from the reference oscillator is frequency-divided to units of 10Hz. This division is performed by the IC5  $\sim$  10 in 6 stages, each in charge of 1/10 division. When the obtained 10Hz signal is used to drive the flip-flop circuit of IC11, a 50% duty square wave of 5Hz is obtained. As shown in the timing chart of Fig. 15, the H level section corresponds to half a cycle of 5Hz, i.e. 0.1 second. Therefore this section is used as a gate signal. Similarly outputs of IC10 and IC11 are combined, and the NAND logic and the differential circuit are combined in the sequential order of Y1 to Y9 as shown in the timing chart. Thus the respective reset, load, and latch pulses are produced. There are two types of reset pulses, A and B, because the SN74196N of the HET counter is for the negative logical input while the SN74LS90N is for the positive logical input. Q24 is a transistor gate for the DH circuit. It is turned on when the DH is off.

#### Latch Circuit and DH Switch

Input pulses are continuously entering the counter circuit. If the counter output is directly transferred to the display, the displayed result will change erratically with each change in the counted result. Such a display cannot be read out in practical use. Therefore the counted results must be retained until the display requires them. The latch circuit is used for this purpose. It is a type of memory circuit which keeps the counted result and sends it to the display upon the reception of a latch signal. Each time the latch signal is delivered, the latch circuit gives to the display the counted value which was obtained while the gate was open before the reception of the latch signal. In the DG-5 the interval between the 2 neighboring latch signals is 0.2 second.

The DH circuit is such that the displayed result remains unchanged until another latch signal arrives. The transistor gate of Q24 is connected in series with the latch signal route and the entry of a latch pulse is interrupted when the DH circuit is on. As shown in Fig. 16, a reverse bias is applied to the Q24 base while the DH circuit is off and there is continuity between the emitter and the collector. When the DH circuit is on, the base loses its bias voltage and continuity is lost between the emitter and the collector. If the main power supply (of TS-520 in this case) is switched on and off while the DH switch is left switched on, a forward bias is applied to the base through the electrolytic capacitor C84 when the main switch is on. During the time constand which is dependent on C84, R100, and R101 (determined to be equivalent to several cycles in counter operation), Q24 is turned on and a correct frequency can be memorized. When the main switch is off, the capacitor C84 is quickly discharged through diode D16.

## 6. Dynamic Display and Multiplexer

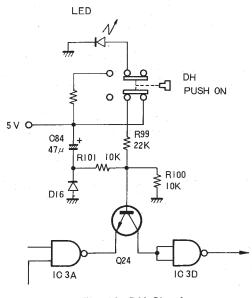

The output from the latch circuit can be displayed for the respective digits when it is delivered to the display through the decoder. This is a static type display circuit, with a block diagram as shown in Fig. 17 (a). Theoretically this type of circuit is very reliable since counters, latches, decoders, and display circuits are independent of each other for each digital unit. However, as the number of digits to be displayed increases, very precious decoder IC's must be installed in a quantity to be displayed increases, very precious decoder IC's must be installed in a quantity which is equal to the number of digits. In addition, since the display section is generally independent of the main printed circuit board, the connections and wiring will be very complex. These are disadvantages of the static type display.

On the other hand there is another type of display, the dynamic dispaly circuit, which is adopted for the DG-5. In this case only one decoder is used. The latches and the display units for the respective digits are controlled through the multiplexer and the counted result is displayed by the time division system. In the circuit shown in Fig. 17 (B), outputs from the respective latches are gathered in the multiplexer. When a scanning control signal is applied to the multiplexer, components of the respective digits are processed by time division switching and sent to the decoder. The multiplexer on the display side is synchro-

Fig. 16 DH Circuitry

nized with that on the latch side for similar switching for each digit. Each type has its own advantages. The disadvantages of this latter type of display are that the multiplexers and the scanning control are required, and that the entire circuit is complex and repair is difficult since the time division switching system is adopted. However, in the case of the DG-5 the number of wire connections to the display is 15 for the dynamic type and 45 for the static type. If in addition the wiring to switches and indicator lamps is taken into acount, the achievement of this same construction with the static type display seems very difficult to achieve.

Fig. 17 Static Display and Dynamic Display

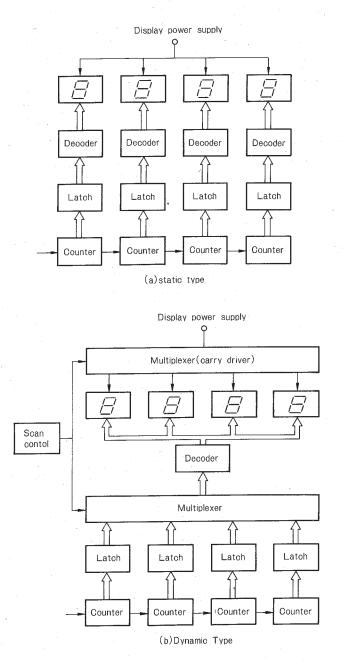

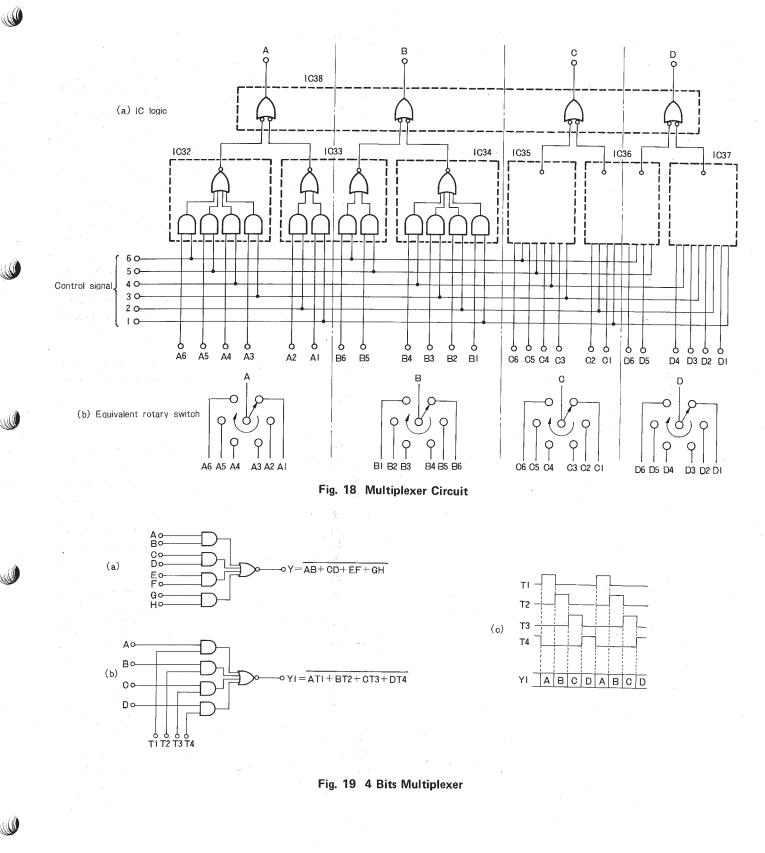

#### Multiplexer

The multiplexer is generally installed on the latch side. In the circuit diagram it is composed of the 7 IC's, IC32 to IC38. The latch output is expressed in the BCD (Binary Coded Decimal) mode and the output for one digit is expressed by the 4 BCD output components, A, B, C, and D. The multiplexer gathers components A (or B, ... ) out of the whole 6 digits in one position and ejects these components A  $\sim$  D synchronized with the scanning control signal by time division switching system. Fig. 18 shows the logica diagram of the circuit blocks that are indicated by the boxes in the circuit diagram. The SN7454N of IC32, 34, 35, and 37 is a 4-input distributor, while the TD3451AP of IC33 and 36 is used as a 2-input 2-circuit distributor. For ease of understanding, Fig. 19 is a logic diagram of SN7454N. As shown in Fig. 19 (a), this IC contains 4 2-input AND circuits and an NOR circuit. When 8 outputs  $A \sim H$  enter, the resultant output Y is as follows:

Y = AB + CD + EF + GH (3)

If these inputs are separated into 2 groups (A, B, C, D signal inputs in one group and T1  $\sim$  4 control signals in the other group), the resultant output Y1 is as follows:

Y1 = AT1 + BT2 + CT3 + DT4 .....(4)

When it is assumed that the signals T1  $\sim$  4 are the control signals scanned in turn as shown in Fig. 19 (c), the output Y1 will come out in the information train of component A for T1, component B for T2, ...., as is obvious from expression (4). The same operation is performed for the 6 digits by the circuit shown in Fig. 19. Since IC does not have any distributor for 6 inputs, outputs from 4-input and 2-input circuits are again combined at IC38 to obtain a function which is equivalent to one obtainable from a 6-input distributor. The control signal in this circuit is switched over in the order of A1, A2, A3, .... at the velocity of 2kHz. Therefore, as shown in Fig. 18 (b), each BCD digit is switched over to another by the rotary switch at the speed of 333Hz. The multiplexer (distributor) on the display side also operates in the same manner. In this case, however, the power supply to the display is merely switched on and off, and a control signal is delivered to the base of the transistor connected in series with the power supply of each display unit, in good timing with the latch side as shown in Fig. 20. Therefore the multiplexer on the display side is used merely to distribute current to the display units.

Ville

Fig. 21 Scanning Control Circuit

⊲⊳

⊲⊳

d⊃

IC 42

-0

-0

#### Scanning Control Circuit

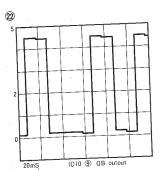

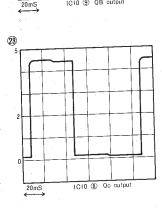

The signals for controlling the multiplexer are generated in the circuit shown in Fig. 21. IC40 receives a 2kHz clock pulse which is obtained from the frequency distributor of the standard oscillator. The DIM siwtch is used to select either base 6 or base 12 counting. The output from IC40 is fed to the BCD decoder of IC41 which generates a negative logic changeover control signal. The operation of this circuit can be grasped from the timing chart in Fig. 22 and the function tables of TD3492BP (IC40) and TD3442AP (IC41) in Figs. 23 and 24. IC40 ordinarily operates as a base 12 counter, and it automatically operates as a base 12 counter when the DIM switch is on (or when either of the reset terminals is at the L level). If the DIM switch is off, one of the 2 reset terminals is at the H level and the other is connected to the QD output line. When counting advances from 0 to 1, ...., and finally to 6, the QD output is immediately at the H level and the C41 is simultaneously reset since the QD line is connected with the reset terminal. When the IC41 is reset, counting is returned to "0" again. That is, this circuit operates as a base 6 counter when the DIM switch is off.

IC41 receives BCD inputs and ejects negative logic outputs at its output terminals,  $0 \sim 9$ . In the DG-5 the 6 outputs from 0 to 5 are used as control signals for the respective digital units. The display driving transistor operates with negative logic pulses and the latch-side multiplexer operates with positive logic pulses. Therefore the respective output circuits are connected with the IC42 inverter to convert the negative logic outputs into positive ones. Thereafter the multiplexer is controlled.

#### **Dimmer Switch**

Current flows in the display while the control signals are present. In the ordinary operating state, the 6-digit base 6 control is exercised. In other words the display unit for each digit is fed 1/6 duty pulse current. If the DIM switch is on in this state, the control is base 12 as described previously. Thus the current flowing in the display is of 1/12 duty and brightness is also reduced to half. This can be understood from the timing chart in Fig. 22.

Fig. 22 Scanning Control Circuit & Timing Chart

## TD3492BP(IC40) COUNT SEQUENCE

## TD3442AP(IC41) FUNCTION TABLE

|                   | -    | OUT | PUT |   |

|-------------------|------|-----|-----|---|

| COUNT             | D    | С   | В   | Α |

| 0                 | L    | L   | L   | L |

|                   | L    | L   | L   | Н |

| 2                 | L    | L   | Н   | L |

| 3                 | L    | Ĺ   | Н   | Н |

| 4                 | L    | Н   | L   | L |

| 5                 | L    | Н   | L   | Н |

| 6                 | н    | L   | L   | L |

| . 7               | Н    | L   | L   | Н |

| la 8 <sup>°</sup> | Н    | L   | Н   | L |

| 9                 | Н    | Ľ   | Н   | H |

| 10                | H    | Н   | L   | L |

| 19 A.H.           | Н    | Н   | Ľ   | Н |

| RESET-            | COUN | т   |     |   |

| RESET | -COUNT |

|-------|--------|

|       |        |

|   | INP   | UTS   | OUTPUTS |   |   |   |  |  |  |  |

|---|-------|-------|---------|---|---|---|--|--|--|--|

| • | Ro(1) | Ro(2) | D       | С | В | А |  |  |  |  |

|   | H     | Н     | L       | L | L | L |  |  |  |  |

|   | L     | Н     |         |   |   |   |  |  |  |  |

|   | Н     | L     | COUNT   |   |   |   |  |  |  |  |

|   | L     | L     |         |   |   |   |  |  |  |  |

|    | INP | UTS |   |     |    |     |       | OUT | PUTS |    |   |       |   |

|----|-----|-----|---|-----|----|-----|-------|-----|------|----|---|-------|---|

| D  | C   | В   | А | 0   |    | 2   | 3     | 4   | 5    | 6  | 7 | 8     | 9 |

| L  | L   | L   | L | L   | H  | Н   | H     | н   | н    | Н  | Н | Н     | Н |

| ·L | L   | · L | Н | н   | L  | Н   | Н     | н   | Н    | Н  | Н | Н     | Н |

| L  | L   | H   | L | н   | H, | L   | Н     | н   | н    | н  | Н | Н     | H |

| L  | L   | Н   | Н | н   | Н  | Н   | Ĺ     | н   | Н    | Ĥ  | Н | Н     | Н |

| L  | н   | L   | L | Η   | H  | Н   | Н     | L   | н    | Н  | Н | Н     | Н |

| L  | н   | L   | Н | Н   | Н  | H   | н     | Н   | L    | Н  | Н | Н     | н |

| L  | Н   | Н   | L | H   | н  | H.  | Н     | H   | ЧНА  | L  | Н | Н     | Н |

| L  | H   | Н   | Н | Н   | Н  | Н   | H     | Η   | н    | H  | L | Η     | Н |

| H  | L   | Ľ   | L | Ĥ   | н  | Н   | Н     | н   | Н    | Η- | H | . L . | н |

| н  | L   | L   | Н | н   | Н  | H.  | Н     | H,  | н    | Н  | н | Н     | L |

| н  | L   | H   | Ŀ | Н   | H  | H   | H     | H   | ۰H   | Н  | н | Н     | H |

| н  | ∘ L | н   | Н | Н   | Н  | H   | Н     | н   | Н    | н  | Ч | Н     | н |

| н  | Н   | Ľ   | L | Н   | н  | Н   | н     | н   | Н    | н  | Н | н     | H |

| Н  | н   | L   | Н | Н   | н  | н   | н     | н   | Н    | Н  | н | н     | н |

| н  | н   | н   | L | H · | н  | н   | н     | н   | Н    | Н  | н | н     | н |

| н  | н   | н   | н | Н   | н  | Н   | H     | н   | н    | Н  | н | н     | н |

|    |     |     |   | -   |    | Fig | j. 24 |     | ÷    |    |   |       |   |

VIII

Ŵ,

g b

с d

Fig. 23

#### SN74247N(IC39) FUNCTION TABLE

| FUNCTION       | TABL | .E  |     |     |     |    |    |     |     |     |       |      |     | · . |          | n             |

|----------------|------|-----|-----|-----|-----|----|----|-----|-----|-----|-------|------|-----|-----|----------|---------------|

| DECIMAL        |      |     | INP | UTS |     | _  | BI |     |     | 0   | UTPUT | rs   |     |     | Display  |               |

| OR<br>FUNCTION | LT   | RBI | D   | С   | , B | A  | ы  | a   | b   | с   | d     | e    | f   | g   | , ,      | f             |

| 0              | Н    | н   | L   | L   | L.  | L  | н  | ON  | ON  | ON  | ON    | ON   | ON  | 0FF | 0        | $\Rightarrow$ |

| 1              | н    | Х   | L   | L   | L   | н  | н  | OFF | ON  | ON  | OFF   | OFF  | OFF | OFF | <u> </u> | e             |

| 2              | н    | Х   | L   | L   | н   | L  | Н  | ON  | ON  | OFF | ON    | ON   | OFF | ON  | 2        |               |

| 3              | Н    | Х   | L   | L   | Н   | н  | н  | ON  | ON  | ON  | ON    | OFF  | OFF | ON  | 3        |               |

| 4              | н    | Х   | L   | н   | L   | L- | н  | OFF | ON  | ON  | OFF   | 0FF  | ON  | ON  | Ч        |               |

| 5              | н    | X   | L   | н   | L   | н  | Н  | ON  | 0FF | ON  | ON    | OFF  | ON  | ON  | 5        |               |

| 6              | н    | Х   | L   | н   | н   | Ŀ  | H  | ON  | OFF | ON  | ON    | ON . | ON  | ON  | 6        |               |

| 7              | н    | Х   | L   | H.  | н   | н  | Н  | ON  | ON  | ON  | OFF   | OFF  | OFF | 0FF | ]        |               |

| 8              | н    | Х   | н   | Ŀ   | Ĺ   | L  | н  | ON  | ON  | ON  | ON    | ON   | ON  | ON  | 8        |               |

| 9              | Н    | Х   | H   | L   | L   | н  | Н  | ON  | ON  | ON  | ON    | OFF  | ON  | ON  | 9        |               |

| 10             | н    | Х   | Н   | L   | н   | L  | н  | OFF | OFF | OFF | ON    | ON   | OFF | ON  | с        |               |

| 11             | Н    | X   | н   | L   | н   | н  | Н  | OFF | OFF | -ON | ON    | OFF  | OFF | ON  | D        |               |

| 12             | н    | Х   | н   | н   | L   | L  | Н  | OFF | ON  | OFF | OFF   | OFF  | ON  | ON  | U        |               |

| 13             | Н    | X   | н   | н   | L   | н  | н  | ON  | OFF | OFF | ON    | OFF  | ON  | ON  | C _      |               |

| 14             | н    | X   | H.  | Н   | Н   | L  | н  | 0FF | 0FF | OFF | ON    | ON   | ON  | ON  | F        |               |

| 15             | Н    | X   | н   | Н   | н   | Н  | H  | OFF | OFF | OFF | 0FF   | OFF  | OFF | OFF |          |               |

| BI             | X    | X   | X   | X   | X   | X  | L  | OFF | 0FF | OFF | 0FF   | OFF  | OFF | OFF |          |               |

| RBI            | Н    | · L | L   | L   | L   | L  | L  | 0FF | OFF | OFF | 0FF   | 0FF  | OFF | OFF |          |               |

| LT             | L    | X   | Х   | Х   | Х   | Х  | н  | 0N  | ON  | ON  | ON    | ON   | ON  | ON  | 8        | ] ·           |

Fig. 25

#### 7. Decoder and Display

#### Decoder

Signals flow within the counter in the BCD mode. Therefore they cannot be displayed immediately after passing through the latch and multiplexer circuits. The decoder is used to convert the BCD signals into the numerals  $0 \sim 9$  readable for us. Since the DG-5 display employs 7-segment LED's, the 7-segment decoder is used. The 7 segments mean that the digit 8 can be divided into 7 segments, and that the other digits  $0 \sim 7$  and 9 can be displayed by selecting those segments that should be lit. Based on the function table of SN74247N in Fig. 25, the open collector transistor is turned on when an input BCD signal enters. Thus the display receives currents to light up the required segments.

The RBI terminal of the decoder receives a control signal for the 10MHz unit. When this terminal is at the L level and the input BCD is "0," the display can be blanked out. Therefore if it is unnecessary to use this unit, as in the case of 7MHz, unwanted "0" is blanked out.

#### Display

The display employs 3 light emitting diodes (LED), each embracing 2 digital units. The size of each digit is 10.16mm x 6.60mm. The LED color is red since that color offers efficient luminance and its brightness, color uniformity, and distribution are all otpimum. In order to obtain color tones comfortable for the yes, the natural dark red of the LED's is softened with violet and light smoke filters.

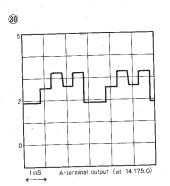

As shown in Fig. 2., the display is connected to the decoder and the same segments of the respective LED's are connected in parallel with each other. The common anode of each LED is connected to the independent 4.5V power supply through the trnasistor switch driver which is provided to each digital unit.

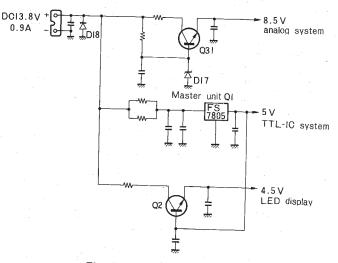

#### 8. Power Circuit

All power for the DG-5 is supplied from the master unit, TS-520S. However, the power cannot be used directly since it contains much ripple voltage. In terms of its power systems, the DG-5 can be roughly divided into the analog circuit system, the TTL. IC system, and the LED display system. As shown in Fig. 26, each system is provided with a stabilized power circuit. The analog system has an 8.5V non-adjustable power circuit stabilized by the zener diode and the transistor. The TTL. IC system employs an exclusively installed 3-terminal regulator since it requires a large current and its voltage regulation must be below 5% though its voltage of 5V is very low. The LED display power can be used in common with the 5V source. However there will be much current difference in such usage when all segments are lit up, and in addition the capacity of 5VIC regulator will almost lose its tolerance. Thus the LED display is also provided with an exclusive power supply. In this case the 5V AVR output is used as the standard stabilized voltage. If the 5V output is switched off, the 4.5V output simultaneously disappears and the LED's go out.

Fig. 26 Power Supply Circuit

6-5

## EXTERNAL VIEW

DG-5

PC BOARD

Counter Unit (X54-1260-00)

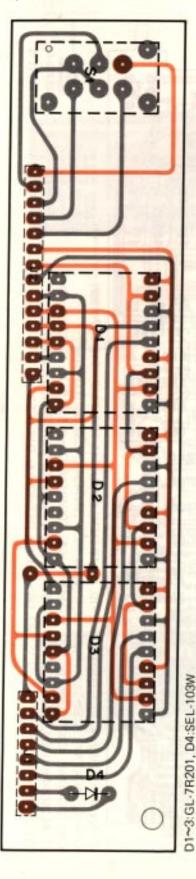

## PC BOARD/PARTS LIST

Display Unit (X54-1270-00)

#### Note 1:

Resistors except the special type (example: cement, metal film, etc.) are not detailed in PARTS LIST. With regard to the value, refer to the schematic diagram or the PC board illustration. Resistors not detailed are carbon type (1/4W or 1/8W). You should give an order for the carbon resistors according to the ways described as follows:

A carbon resistor's part number is example RD14BY 2E 222J

1, Kinds of the carbon resistor

RD14BY

2. Wattage

1/4W → 2E 1/8W → 2B

3. Resistance value

|   | TRA L | F  |  |

|---|-------|----|--|

| - | 0.00  | Į. |  |

|   | o w   | a. |  |

T: Britain

Significant figure Multiplier

Example:

| 221 | + | 22012  |

|-----|---|--------|

| 222 | + | 2.2kΩ  |

| 223 | + | 22kΩ   |

| 224 | + | 220k Ω |

| 225 | + | 2.2MΩ  |

4. Tolerance

No K:

J = ±5% (Gold color) K = ±10% (Silver color)

| te | 2:   |    |        |  |

|----|------|----|--------|--|

| U. | S.A. | W: | Europe |  |

# **PARTS LIST**

| Ref. No | p. Parts No.               | Description                                            | Remai  |         | . No. | Parts No.                  |                    |                                  |

|---------|----------------------------|--------------------------------------------------------|--------|---------|-------|----------------------------|--------------------|----------------------------------|

|         | CA                         | PACITOR/SEMICONDUCTOR                                  |        | C7      |       |                            |                    | Description                      |

| C1      | CK45F1H103                 |                                                        |        |         |       | C-90-0262-05               | Ceram              | 0.047µ 2500V                     |

|         |                            |                                                        |        | C9      |       | CK45B1H331                 |                    | ic 330pF ±10%                    |

| Q1      | V30-0158-05                | IC FS-7805                                             |        | C10     |       | CK45F1H1032                |                    | c 0.01µF +80%, -20%              |

| Q2      | V04-0046-05                | Transistor 2SD235(Y)                                   | 1      | C11,    | 12    | CK45F1H2232                |                    | c 0.022µF+80%, -20%              |

|         |                            |                                                        |        | C13     |       | CS15E1A100N<br>C90-0262-05 |                    | 10μF 10WV                        |

|         |                            | MISCELLANEOUS                                          |        | C14     |       | CE04W1A221                 | Cerami             |                                  |

|         | A01-0709-22                | Case                                                   | - T .  | C15     |       | CE04W1C220                 | Electro            | lytic 220µF 10WV                 |

| -       | A20-2307-15                | Panel                                                  | 4      | C16     |       | C90-0262-05                | Cerami             | lytic 22µF 16WV                  |

| -       | A23-1405-03                | Rear panel                                             | \$     | C17     |       | CE04W1A101                 |                    |                                  |

|         |                            |                                                        |        | C18     |       | CC45SL1H470                | J Cerami           | lytic 100µF 10WV                 |

|         | B03-0503-24                | Switch mask                                            | \$     | C19     |       | CK45B1H102K                |                    |                                  |

| _       | B10-0604-04                | Front glass                                            | 고<br>☆ | C20     |       | CE04W0J331                 |                    |                                  |

| _       | B11-0402-04                | Filter                                                 |        | C21     |       | CK45B1H331K                | Ceramic            | ytic 330µF 6.3WV                 |

| _       | B40-2414-04                | Name plate                                             | - ×    | C22     |       | CK45F1H473Z                | Ceramic            |                                  |

|         | B43-0607-04                | Badge (TRIO)                                           | м<br>Ф | C23     |       | CC45SL1H470                | Ceramic            | 100%, -20%                       |

| - 1     | B43-0608-04                | Badge (KENWOOD)                                        | м<br>ф | C24     |       | CC45CH1H050                | D Ceramic          | 20%                              |

| -       | B46-0058-00                | Warranty card (K only)                                 |        | C25     |       | CK45F1H223Z                | Ceramic            |                                  |

|         | B50-2536-00                | Operating manual (K, W)                                | \$     | C26     |       | CK45F1H103Z                | Ceramic            |                                  |

| -       | B50-2537-00                | Operating manual (T)                                   | 4      | C27     |       | CC45SL1H470J               | Ceramic            |                                  |

| -       |                            |                                                        |        | C28     |       | CK45B1H102K                | Ceramic            | 1000pF ± 10%                     |

| -       | E08-0203-25                | 2P connector socket (Receptacle)                       |        | C29     |       | СК45В1Н331К                | Ceramic            |                                  |

|         | E09-0203-25                | 2P connector socket (Plug) X 2                         |        | C30     | ·     | CK45F1H223Z                | Ceramic            | 0.022µF +80%, -20%               |

|         | E14-0061-05                | Phono plug (Red) X 2                                   | 4      | C31     |       | CC45CH1H050                | Ceramic            | 5pF ±0.5pF                       |

|         | E14-0062-05                | Phono plug (White) X 2                                 | \$     | C32     |       | CC45SL1H470J               | Ceramic            | 47pF ±5%                         |

|         | E14-0063-05                | Phono plug (Black) X 2                                 | ☆      | C33     |       | CK45F1H103Z                | Ceramic            | 0.01µF +80%, -20%                |

| 1       | E14-0115-05                | Phono plug (Gray) X 3                                  |        | C34     |       | CK45F1H223Z                | Ceramic            | 0.022µF +80%, -20%               |

|         | E91-0017-05                | Clip (Red)                                             |        | C35     |       | CC45SL1H470J               | Ceramic            | 47pF ±5%                         |

|         | E91-0018-05                | Clip (Black)                                           |        | C36     |       | CK45B1H102K                | Ceramic            | 1000pF ± 10%                     |

| 1.      |                            |                                                        |        | C37, 3  | 8     | CK45F1H103Z                | Ceramic            | 0.01µF +80%, -20%                |

|         | F15-0605-04                | Blinding plate                                         | \$     | C40     |       | CC45CH1H010C               |                    | 1pF ±0.25pF                      |

| 1       | F20-0078-05<br>F29-0014-05 | Insulating plate                                       |        | C40     |       | C45SL1H391J                | Ceramic            | 390pF ±5%                        |

|         | 29-0014-05                 | Insulating washer                                      |        | C42     |       | C45SL1H101J                | Ceramic            | 100pF ±5%                        |

|         | 101-2530-04                | Deal                                                   |        | C43     |       | C45F1H103Z                 | Ceramic            | 0.01µF +80%, -20%                |

|         |                            | Packing case (Inside) (T)                              | 4      | C44     |       | C45SL1H680J<br>C45SL1H101J | Ceramic            | 68pF ±5%                         |

|         |                            | Packing case (Inside) (K, W)                           | 4      | C45~4   | 7 0   | C45CH1H330J                | Ceramic            | 100pF ±5%                        |

|         |                            | Carton case (Outside) (T)                              |        | C48, 4  |       | K45F1H103Z                 | Ceramic            | 33pF ±5%                         |

|         | 112-0460-04                | Carton case (Outside) (K, W)                           |        | C50     |       | 90-0262-05                 | Ceramic            | 0.01µF +80%, -20%                |

|         |                            | Styrene foam cushion (A) X 2                           | 1      | C51     |       | C45SL1H121J                | Ceramic            | 0.047µF 25WV                     |

|         |                            | Styrene foam cusion (B)<br>Protection bag (Attachment) | \$     | C52     | l c   | C45SL1H271J                | Ceramic            | 120pF ±5%                        |

|         | 125-0106-04                | Protection bag (Attachment)<br>Protection bag          |        | C53     | lč    | C45CH1H100D                | Ceramic            | 270pF ±5%                        |

|         |                            | Protection bag<br>Protection bag (Leg X 2, screw X 2)  |        | C54, 5  | 5 C   | 90-0262-05                 | Ceramic            | 10pF ±0.5pF                      |

|         |                            | Leg A 2, screw X 2)                                    | 1. 1   | C56     |       | K45F1H130Z                 | Ceramic<br>Ceramic | 0.047µF 25WV                     |

| IL      | 02-0069-05                 | Leg (Small X 2)                                        |        | C57     |       | C45SL1H121J                | Ceramic<br>Ceramic | 0.01µF +80%, -20%                |

|         |                            | Leg (Rubber X 4)                                       |        | C58     | c     | C45SL1H271J                | Ceramic            | 120pF ±5%                        |

|         | 1                          | Bushing (Knob)                                         | 4      | C59     | C     | C45SL1H121J                | Ceramic            | 270pF ±5%                        |

|         |                            | - · ··,                                                |        | C60     | C     | K45F1H103Z                 | Ceramic            | 120pF ±5%                        |

| ĸ       | 27-0035-04                 | Knob                                                   |        | C61, 62 |       | 0-0262-05                  | Ceramic            | 0.01µF +80%, -20%                |

|         |                            |                                                        |        | C63     | CI    | <45F1H103Z                 | Ceramic            | 0.047µF 25WV                     |

| N       | 09-0601-05                 | Screw X 2                                              |        | C64     | 00    | C45CH1H560J                | Ceramic            | 0.01µF +80%, -20%                |

|         |                            |                                                        |        | C65     | CC    | 245SL1H391J                | Ceramic            | 56pF ±5%                         |

| X       | 54-1260-00                 | Counter unit                                           | ☆      | C56     |       | 45CH1H470J                 | Ceramic            | 390pF ±5%<br>47pF ±5%            |

| X       | 54-127 <b>0-00</b> [       | Display unit                                           | \$     | C67     | Ck    | (45F1H103Z                 | Ceramic            |                                  |

|         |                            |                                                        |        | C68     | CC    | 45CH1H010C                 | Ceramic            | 0.01µF +80%, -20%<br>1pF ±0.25pF |

|         |                            |                                                        |        | C69     | CC    | AFOLIALIATO                | Ceramic            | till op 1                        |

|         |                            |                                                        |        | C70     | Ск    | 45B1H471K                  | Ceramic            | 15pF ±5%<br>470pF ±10%           |

|         | <b>.</b>                   |                                                        |        | C71, 72 | C9    | 0-0262-05                  |                    | 0.047µF 25WV                     |

| UNTE    | R UNIT (X                  | 54-1260-00)                                            |        | C73     |       | 45SL1H470J                 | Ceramic            | 47pF ±5%                         |

|         |                            |                                                        |        | C74     | 1     | 16814331W                  |                    |                                  |

C74 C75 C76 C77 C78 C79 C80 C81

## COUNTER UNIT (X54-1260-00)

| Ref. No.  | Parts No.                  | Description                                                    | Re-<br>marks |  |  |  |  |  |  |

|-----------|----------------------------|----------------------------------------------------------------|--------------|--|--|--|--|--|--|

| CAPACITOR |                            |                                                                |              |  |  |  |  |  |  |

| C1        | C91-0411-05                | Metallized polyester 0.22µF                                    |              |  |  |  |  |  |  |

| C2<br>C3  | CC45SL2H330J<br>CE04W1H010 | 5-141115 66pt ±5%                                              | \$           |  |  |  |  |  |  |

| C4        | CK45F1H103Z<br>CE04W1A221  | Electrolytic 1 $\mu$ F 50WV<br>Ceramic 0.01 $\mu$ F +80%, -20% |              |  |  |  |  |  |  |

|           | - 1                        | Electrolytic 220µF 10WV<br>Ceramic 330pF ±10%                  |              |  |  |  |  |  |  |

|      | CK45B1H102               |     | Cerami    | c 10          | DOpF:          | ± 10%          | 1    |   |

|------|--------------------------|-----|-----------|---------------|----------------|----------------|------|---|

|      | CK45B1H331I              |     | Ceramic   | ° 33(         | )<br>pF :      | ± 10%          |      |   |

|      | CK45F1H2232              |     | Ceramic   | 0.0           | 22µF           | +80%, -2       | 0%   |   |

|      | CC45CH1H050              | D   | Ceramic   | 5 5pf         | = ' <u>-</u>   | ±0.5pF         | 0/0  |   |

|      | CC45SL1H470              | J.  | Ceramic   | ÷ 47p         |                | ± 5%           | [    |   |

|      | CK45F1H103Z              |     | Ceramic   |               |                | +80%, -20      | 10/  |   |

|      | CK45F1H223Z              |     | Ceramic   | 0.0           | 22 <i>u</i> F  | +80%, -20      | 0.02 |   |

|      | CC45SL1H470              | J . | Ceramic   | 47p           |                | :5%            | J%   |   |

|      | CK45B1H102K              |     | Ceramic   |               | 0pF±           |                | ļ    |   |

| 3    | CK45F1H103Z              |     | Ceramic   | 0.0           | μF +           | -80%, -20      | 0/   |   |

|      | CC45CH1H010              | С   | Ceramic   |               |                | 0.25pF         | %    |   |

|      | CC45SL1H391.             | J   | Ceramic   |               | pF ±           |                |      |   |

|      | CC45SL1H101              |     | Ceramic   |               | pF ±           |                |      |   |

|      | CK45F1H103Z              |     | Ceramic   |               |                | 80%,209        |      |   |

|      | CC45SL1H680.             |     | Ceramic   | 68p           |                | 5% ~20         | %    |   |

|      | CC45SL1H101J             |     | Ceramic   | 100           |                | 5%             |      |   |

|      | CC45CH1H330.             | J   | Ceramic   |               | = ±            |                |      |   |

|      | CK45F1H103Z              |     | Ceramic   | 0.01          |                |                |      |   |

| 1    | C90-0262-05              |     | Ceramic   | 0.01          | μг +<br>7μF 2  | 80%, -20%      | 6    |   |

| - 14 | CC45SL1H121J             |     | Ceramic   |               | νμε 2<br>νΕ ±! |                |      |   |

|      | CC45SL1H271J             |     | Ceramic   |               | )F ± {         |                | 1    |   |

|      | CC45CH1H1000             |     | Ceramic   |               |                |                |      |   |

|      | 0262-05                  | - 1 | Ceramic   |               | ±              |                |      |   |

| 0    | CK45F1H130Z              | 1   | Ceramic   | 0.04          | 7μF 2          | SWV            |      |   |

| 0    | CC45SL1H121J             | - 1 | Ceramic   | 120-          | /F +8          | 30%, -20%      |      |   |

|      | C45SL1H271J              |     | Ceramic   |               | F ±5           |                |      |   |

| 0    | C45SL1H121J              |     | Ceramic   |               | F ±5           |                |      |   |

| 0    | K45F1H103Z               |     | Ceramic   |               | F ±5           |                |      |   |

|      | 90-0262-05               |     | eramic    | 0.01          | (F +8          | 0%, -20%       | 1 .  |   |

|      | K45F1H103Z               |     | Ceramic   | 0.047         | μF 2           | 5WV            |      |   |

| c    | C45CH1H560J              |     | eramic    | 0.01          |                | 0%,20%         |      |   |

| c    | C45SL1H391J              |     | eramic    | 56pF          |                |                |      |   |

| c    | C45CH1H470J              |     | eramic    | 390pi         |                |                |      |   |

| c    | K45F1H103Z               |     | eramic    | 47pF          |                | %              |      |   |

|      | C45CH1H010C              |     | eramic    | 0.01µ         |                | 0%, -20%       |      |   |

| c    | C45CH1H150J              | 1   | eramic    | 1pF           |                | 25pF           |      |   |

| c    | K45B1H471K               |     | eramic    | 15pF          |                | -              | [    |   |

|      | 90-0262-05               |     | eramic    | 470pF         |                |                |      |   |

|      | C45SL1H470J              |     | eramic    | 0.047         |                |                |      |   |

| C    | K45B1H331K               |     |           | 47pF          | ± 5%           |                |      |   |

|      | C45CH1H010C              |     | eramic    | 330pF         |                |                |      |   |

| С    | <45B1H102K               |     | eramic    | 1pF           | ±0.:           | 25pF           |      |   |

| c    | 292M1H104K               |     | Pramic    | 1000p         |                |                |      |   |

| C    | (45B1H102K               |     | ylar      | 0.1µF         |                |                |      |   |

| cr   | 92M1U104K                |     | ramic     | 1000p         | F ± 10         | %              |      |   |

| C K  | 292M1H104K<br>(45B1H102K |     | vlar      | 0.1μF         | ±10            | %              |      |   |

| 00   | 92M1U102K                |     | ramic     | 1000pl        | = ± 10         | %              |      |   |

|      | 92M1H104K                |     | /lar      | <b>0</b> .1μF | ± 10           | %              |      |   |

|      | 45B1H102K                |     | ramic     | 1000pf        |                |                |      |   |

| 00   |                          |     | ramic     | 22pF          | ±5%            |                |      |   |

| CE   | 04W1A470                 | Ele | ctrolytic | 47μF          | 10W            |                |      |   |

| υĸ   | 45F1H103Z                | Cei |           |               |                | %, <b>–20%</b> |      |   |

|      |                          |     |           |               |                | . 20%          |      |   |

|      |                          |     |           |               |                |                |      | Ĩ |

# PARTS LIST

|   | Ref. No.           | Parts No.                             | Description                                     | Re-<br>marks | Ref. No.           | Parts    |

|---|--------------------|---------------------------------------|-------------------------------------------------|--------------|--------------------|----------|

|   | C86                | CE04W1C220                            | Electrolytic 22µF 16WV                          |              | D1~5               | V11-037  |

|   | C87                | CQ92M1H104K                           | Mylar 0.1µF ±10%                                |              | D6~11              | V11-005  |

|   | C88                | CE04W1E470                            | Electrolytic 47µF 25WV                          |              | D12~16             | V11-037  |

|   | C89                | CQ92M1H104K                           | Mylar 0.1µF ±10%                                |              | D17                | V11-024  |

|   | C90                |                                       |                                                 |              | D18                | V11-027  |

|   | C91, 92            | CE04W1A101                            | Electrolytic 100µF 10WV                         |              | D19                | V11-037  |

|   | C93                | CK45F1H473Z                           | Ceramic 0.047µF+80%, -20%                       |              |                    |          |

|   | C94                | CE04W1C220                            | Electrolytic 22µF 16WV                          |              |                    | 1        |

|   | C95                | CQ92M1H104K                           | Mylar $0.1\mu F \pm 10\%$                       |              | TC1                | C05-004  |

|   | C96                | CC45CH1H100D                          | Ceramic 10pF ±0.5pF                             |              |                    | 1 77 040 |

|   | C97                | CC45SL1H101J                          | Ceramic 100pF ± 5%<br>Ceramic 0.01µF +80%, -20% |              | X1                 | L77-048  |

|   | C98                | CK45F1H103Z                           |                                                 |              | L1                 | L40-100  |

|   | C99                | CC45SL1H330J<br>CK45F1H103Z           | Ceramic 33pF ±5%<br>Ceramic 0.01µF +80%, -20%   |              | L2~4               | L40-100  |

|   | C10                | CK45F1H1032                           |                                                 |              | L5                 | L40-151  |

|   | C101<br>C102       | CC45SL1H470J                          | Ceramic 47pF ±5%                                |              | L6~8               | L40-471  |

|   | C102               | 0040021114700                         |                                                 | I            | L9, 10             | L40-101  |

|   |                    |                                       | RESISTOR                                        |              | L11, 12            | L40-471  |

|   | B1~131             | RD14CY2B000J                          | Carbon 000Ω ±5% 1/8W                            |              | L14, 15            | L40-100  |

|   |                    |                                       | Refer to schematic diagram,                     |              | ∟16                | L33-060  |

|   |                    |                                       | on the value.                                   |              |                    |          |

|   | R26, 41,           |                                       |                                                 |              | T1, 2              | L34-062  |

|   | R56~58,80          | )                                     |                                                 |              |                    |          |

|   | R125, 126          | RS14AB3D120J                          | Metallized film resistor                        |              |                    |          |

|   |                    |                                       | 12Ω +5% 2W                                      |              | S1 .               | S40-205  |

|   | R127               | RS14AB3A100J                          | Metallized film resistor                        |              | S2                 | S31-100  |

|   |                    |                                       | 10Ω ±5% 2W                                      |              | S3                 | S31-140  |

|   | R129               | RS14AB3D8R2J                          | 1 .                                             |              |                    | 1        |

|   |                    | 1                                     | 8.2Ω ±5% 2W                                     |              |                    | T        |

|   |                    | SEM                                   | ICONDUCTOR                                      |              |                    | E02-010  |

|   |                    |                                       |                                                 |              | —                  | E13-016  |

|   | 1C1                | V30-0181-05                           | IC SN74S00N                                     |              | - 1                | E18-020  |

|   | 1C2~4              | V30-0132-05                           |                                                 |              | -                  | E23-004  |

|   | 1C5~10             | V30-1005-26                           | IC SN74LS90N<br>IC TD3472AP                     | <u>а</u> .   |                    | E40-081  |

|   | 1C11               | V30-0131-05                           | IC TD3472AP<br>IC SN74196N                      | \$           |                    | E40-141  |

|   | IC12               | V30-1009-16<br>V30-1005-26            | IC SN74LS90N                                    | и<br>Ф       |                    |          |